October 1987 Revised March 2002

# CD4007C Dual Complementary Pair Plus Inverter

#### **General Description**

FAIRCHILD

SEMICONDUCTOR

The CD4007C consists of three complementary pairs of Nand P-channel enhancement mode MOS transistors suitable for series/shunt applications. All inputs are protected from static discharge by diode clamps to V<sub>DD</sub> and V<sub>SS</sub>.

For proper operation the voltages at all pins must be constrained to be between  $V_{SS}$  – 0.3V and  $V_{DD}$  + 0.3V at all times.

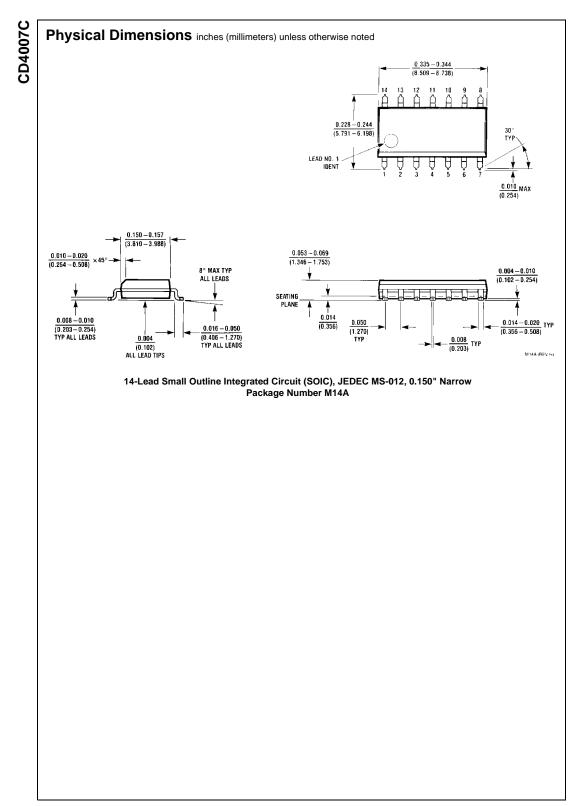

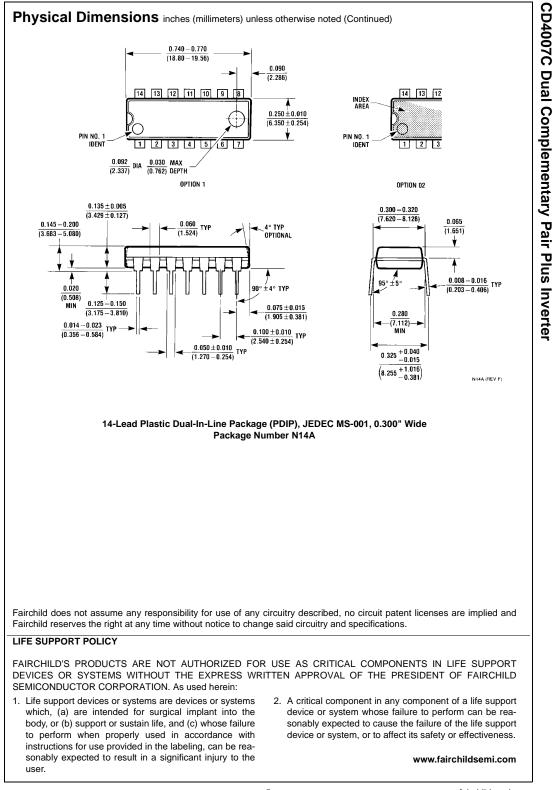

#### **Ordering Code:**

|                                                                                                           | -              | -                                                                            |  |  |  |

|-----------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------|--|--|--|

| Order Number                                                                                              | Package Number | Package Description                                                          |  |  |  |

| CD4007CM                                                                                                  | M14A           | 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow |  |  |  |

| CD4007CN N14A 14-Lead Plastic Dual-In-                                                                    |                | 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide       |  |  |  |

| Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code. |                |                                                                              |  |  |  |

**Features**

■ Wide supply voltage range: 3.0V to 15V

■ High noise immunity: 0.45 V<sub>CC</sub> (typ.)

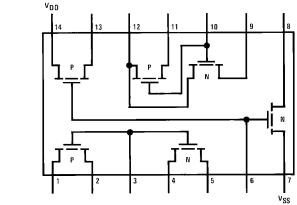

#### **Connection Diagram**

Note: All P-channel substrates are connected to  $V_{DD}$  and all N-channel substrates are connected to  $V_{SS}$ .

**Top View**

www.fairchildsemi.com

### Absolute Maximum Ratings(Note 1)

| Voltage at Any Pin                  | $V_{SS}$ –0.3V to $V_{DD}$ +0.3V        |

|-------------------------------------|-----------------------------------------|

| Operating Temperature Range         | -55°C to +125°C                         |

| Storage Temperature Range           | -65°C to +150°C                         |

| Power Dissipation (P <sub>D</sub> ) |                                         |

| Dual-In-Line                        | 700 mW                                  |

| Small Outline                       | 500 mW                                  |

| Operating V <sub>DD</sub> Range     | $\rm V_{SS}$ +3.0V to $\rm V_{SS}$ +15V |

| Lead Temperature                    |                                         |

| (Soldering, 10 seconds)             | 260°C                                   |

Note 1: This device should not be connected to circuits with the power on because high transient voltages may cause permanent damage.

## **DC Electrical Characteristics**

|                  |                      |                                                     | Limits |     |       |      |       |        |       |     |       |      |  |

|------------------|----------------------|-----------------------------------------------------|--------|-----|-------|------|-------|--------|-------|-----|-------|------|--|

| Symbol           | Parameter            | Conditions                                          | –55°C  |     | +25°C |      |       | +125°C |       |     | Units |      |  |

|                  |                      |                                                     | Min    | Тур | Max   | Min  | Тур   | Max    | Min   | Тур | Max   |      |  |

| IL.              | Quiescent Device     | $V_{DD} = 5.0V$                                     |        |     | 0.05  |      | 0.001 | 0.05   |       |     | 3.0   | μA   |  |

|                  | Current              | $V_{DD} = 10V$                                      |        |     | 0.1   |      | 0.001 | 1.0    |       |     | 6.0   | μА   |  |

| PD               | Quiescent Device     | $V_{DD} = 5.0V$                                     |        |     | 0.25  |      | 0.005 | 2.5    |       |     | 15    | μW   |  |

|                  | Dissipation Package  | $V_{DD} = 10V$                                      |        |     | 1.0   |      | 0.001 | 10     |       |     | 60    | μνν  |  |

| V <sub>OL</sub>  | Output Voltage       | $V_{DD} = 5.0V$                                     |        |     | 0.05  |      | 0     | 0.01   |       |     | 0.05  | v    |  |

|                  | LOW Level            | $V_{DD} = 10V$                                      |        |     | 0.05  |      | 0     | 0.01   |       |     | 0.05  | v    |  |

| V <sub>OH</sub>  | Output Voltage       | $V_{DD} = 5.0V$                                     | 4.95   |     |       | 4.95 | 5.0   |        | 4.95  |     |       | v    |  |

|                  | HIGH Level           | $V_{DD} = 10V$                                      | 9.95   |     |       | 9.95 | 10    |        | 9.95  |     |       | v    |  |

| V <sub>NL</sub>  | Noise Immunity       | $V_{DD} = 5.0V, V_{O} = 3.6V$                       |        |     | 1.5   |      | 2.25  | 1.5    |       |     | 1.4   | v    |  |

|                  | (All inputs)         | $V_{DD} = 10V, V_{O} = 7.2V$                        |        |     | 3.0   |      | 4.5   | 3.0    |       |     | 2.9   | v    |  |

| V <sub>NH</sub>  | Noise Immunity       | $V_{DD} = 5.0V, V_{O} = 0.95V$                      | 3.6    |     |       | 3.5  | 2.25  |        | 3.5   |     |       | v    |  |

|                  | (All Inputs)         | $V_{DD} = 10V, V_{O} = 2.9V$                        | 7.1    |     |       | 7.0  | 4.5   |        | 7.0   |     |       | v    |  |

| I <sub>D</sub> N | Output Drive Current | $V_{DD} = 5.0V, V_{O} = 0.4V, V_{I} = V_{DD}$       | 0.75   |     |       | 0.6  | 1.0   |        | 0.4   |     |       | mA   |  |

|                  | N-Channel            | $V_{DD}=10V,\ V_O=0.5V,\ V_I=V_{DD}$                | 1.6    |     |       | 1.3  | 2.5   |        | 0.95  |     |       | mA   |  |

| I <sub>D</sub> P | Output Drive Current | $V_{DD} = 5.0$ V, $V_{O} = 2.5$ V, $V_{I} = V_{SS}$ | -1.75  |     |       | -1.4 | -4.0  |        | -1.0  |     |       | mA   |  |

|                  | P-Channel            | $V_{DD} = 10V, \ V_O = 9.5V, \ V_I = V_{SS}$        | -1.35  |     |       | -1.1 | -2.5  |        | -0.75 |     |       | IIIA |  |

| Ц                | Input Current        |                                                     |        |     |       |      | 10    |        |       |     |       | pА   |  |

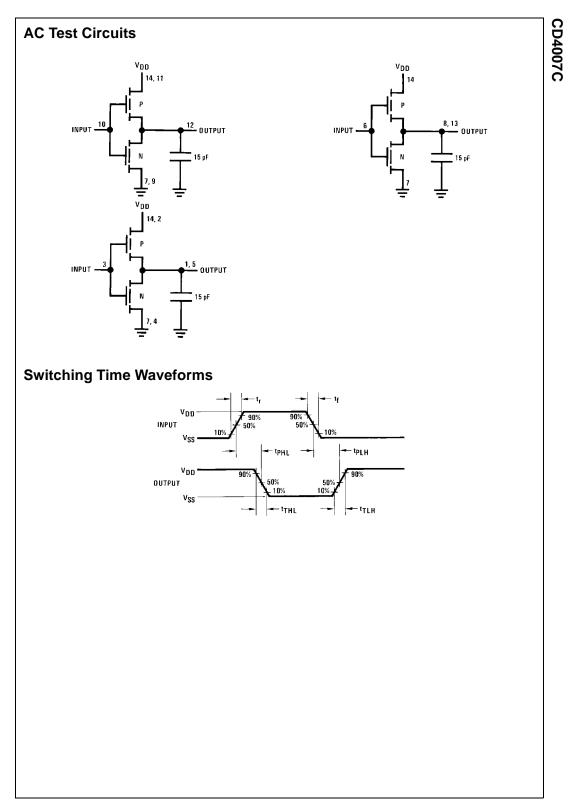

## AC Electrical Characteristics (Note 2)

| Symbol                              | Parameter              | Conditions             | Min | Тур | Max | Units |

|-------------------------------------|------------------------|------------------------|-----|-----|-----|-------|

| t <sub>PLH</sub> = t <sub>PHL</sub> | Propagation Delay Time | V <sub>DD</sub> = 5.0V |     | 35  | 75  | ns    |

|                                     |                        | $V_{DD} = 10V$         |     | 20  | 50  |       |

| t <sub>TLH</sub> = t <sub>THL</sub> | Transition Time        | V <sub>DD</sub> = 5.0V |     | 50  | 100 | ns    |

|                                     |                        | $V_{DD} = 10V$         |     | 30  | 50  |       |

| CI                                  | Input Capacitance      | Any Input              |     | 5   |     | pF    |

Note 2: AC Parameters are guaranteed by DC correlated testing.

www.fairchildsemi.com

www.fairchildsemi.com